-

Liquid crystal flat panel display - 2. LCD Interface 종류 및 Driver IC 1 (RGB, I80, M68)[출처] Liquid crystal flat panel display - 2. LCD Interface 종류 및 Driver IC 1 (RGB, I80, M68)Electron/Etc. 2020. 7. 6. 17:31

Liquid crystal flat panel display

Liquid crystal flat panel display 두 번째 시간입니다. 지난 호 에는 FPD 종류 및 TFT-LCD 구조에 대해 소개 했고, 이번 호 에서는 조금 더 LCD 속으로 들어가서 Instruction Data및 display Data를 LCD에 전송하는 방식에 따른 분류를 소개 하겠습니다. LCD에 점 하나 찍고 사진 한 장을 Display 하는 것에도 각 Interface마다 각각 다른 방법을 사용한다는 것을 알 수 있을 것입니다. 많은 종류 중에 현재 많이 사용하고 있는 GRB, CPU(I80, M68)방식에 대해서 이번 호 에서 다룰 것이며 Serial 방식(MDDI, MIPI, SPI, I2C)은 다음 호 에 이어서 연재 하도록 하겠습니다.

연재 순서

1. FPD 종류 및 TFT-LCD 구조

2. LCD Interface 종류 및 Driver IC 1 (RGB, I80, M68)

3. LCD Interface 종류 및 Driver IC 2 (MDDI, MIPI, SPI, I2C)

4. Pxa270 + 2700G 를 이용한 여러 Interface 제어

5. Luminance 와 Pattern Generate 를 이용한 LCD 테스트

Mobile interface의 종류

Mobile interface의 종류로는 CPU interface(I80, M68), RGB interface, SPI interface, MDDI interface, MIPI interface 등 종류에 따라 제어 신호들이 다르다.

CPU interface의 경우 WR(Write), RD(Read), RS(Command/Data), CS(Chip select) 등의 제어 신호들로 구성되어 있고 driver IC 내부에 RAM을 사용한다. RGB interface의 경우 VSYNC(Vertical Sync), HSYNC(Horizontal Sync), ENABLE, DOTCLK(Clock) 등의 제어 신호를 사용하고 driver IC의 초기화를 위해 serial 제어 신호를 사용한다. serial interface의 경우 SDI, SDO, SCL 등의 신호들을 통해 data를 serial로 전송하며 최근에는 data를 빠르게 전송하고 신호선을 대폭 감소한 MDDI와 같은 serial link type의 serial interface도 나오고 있다.

Interface 종류

사용되는 제어 신호

CPU interface

WR, RD, RS, CS

RGB interface

VSYNC, HSYNC, ENABLE, DOTCLK

Serial interface

SDI, SDO, SCL, CS

표1. Interface 종류에 따른 제어 신호

CPU interface

CPU interface는 MPU interface라고도 불리며 80계열(intel) 또는 68계열(Motorola)의 MPU(Micro Processor Unit)의 제어 신호에 따라 data를 전송하는 interface 방식이다. CPU interface 방식의 경우 RS 신호에 따라 명령어(command)와 display data가 나뉘어져서 전송한다.

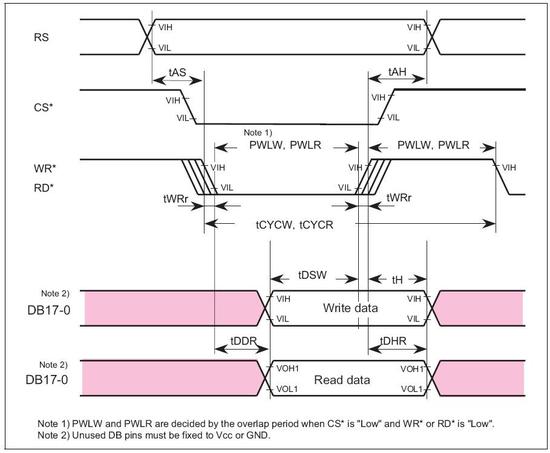

그림1은 CPU interface를 설명하기 위한 timing도이다. CS는 chip select 신호로 low일 때 chip이 동작되도록 하는 신호이고 WR은 write 신호로 low에서 high로 변할 때, 즉 rising할 때, data를 display RAM에 write한다. 이 때 RS는 high이기 때문에 RAM에 저장되는 data는 display data가 된다. 다음으로 명령어를 register에 write하기 위해 RS 신호를 low로 하고 이 때, write 신호를 address data와 command data에 맞게 latch 시킨다. 마지막으로 display RAM에 저장한 data를 읽어 오기 위해 RS 신호는 high로 맞추고 이 때 display data는 WR 신호에 맞게 내보내게 된다.

그림 1. CPU interface 제어 신호 timing도

Driver IC spec을 확인해보면 CPU interface Type에서도 Bus line 구성 방법에 따라서 여러 Interface를 선택할 수 있다.

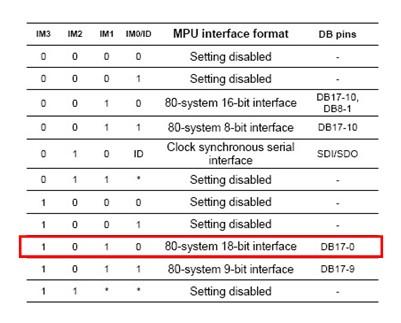

그림2는 driver IC의 interface를 설정하기 위해 IM3-0 signal을 설정한 부분이다. 보통 많이 사용 하는 80-system으로 테스트 모듈은 18-bit interface를 사용하게 되므로 그림2와 같이 IM3-0을 1010으로 설정한다. 다른 interface를 사용할 경우 그림3 ~ 그림5 에 나와 있는 Interface에 맞게 IM3-0 신호를 해당 interface에 맞게 설정하면 된다.

테스트 용으로 사용한 1.9 inch 모듈은 내부적으로 IM0 = 0, IM1 = 1, IM2 = 0으로 설정되어 있고, IM3 Signal을 외부로 빼서 사용자가 선택하도록 설정 되어있다. 그렇기 때문에 IM3이 0이면 16bit, IM3이 1이면 18bit로 설정 된다.

그림 2. IM3-0 signal 설정

CPU Instruction Interface 설정

LCD 모듈을 설계할 당시 Driver IC spec 을 보고 사용할 내부 Interface를 선택 하는데

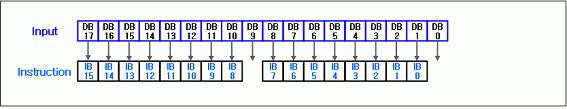

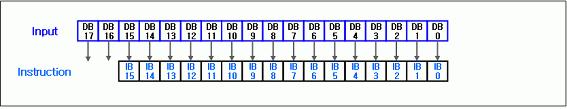

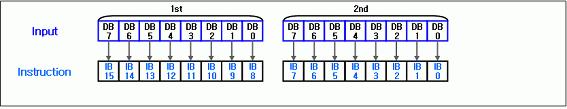

아래 그림3~그림5는 Register Instruction을 설정하는 방법을 나타낸 것이다. DB0~DB17은 CPU에서 나오는 Data Bus이며 IB0~IB15는 LCD 모듈 쪽으로 들어가는 신호로 생각하면 된다.

그림3은 18bit Interface에서 많이 사용하는 방식으로 18bit bus에 16bit Register 값을 넣어주시기 위해 DB0, DB9의 신호를 빼고 받아들이는 방식을 선택하고 있다.

그림 3. CPU Interface TYPE1

그림4의 경우는 16bit Interface에서 많이 사용하며 하위비트부터 16bit를 차례로 사용하여 구성한다.

그림 4. CPU Interface TYPE2

그림5의 경우는 8bit Interface로 Data bus를 DB0~DB7까지 8개 라인을 사용한다. Register Data는 보통 16bit를 사용하기 때문에 LCD 모듈 쪽으로 8bit씩 두 번 전송하게 된다.

그림 5. CPU Interface TYPE3

Driver IC register 설정

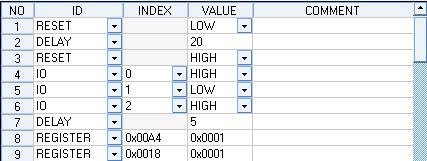

Register setting은 Index에 16진수(Hex) 네 자리로 주소를 설정하고 Value에 16진수(Hex) 네 자리로 값을 설정한다. Index에 주소를 입력할 때와 Value에 값을 입력할 때는 0x0000 형식으로 넣는다.

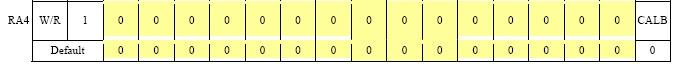

Register를 설정 할 때, driver IC의 Reset 후에 CALB를 1로 설정 해야 한다. 그림 6과 같이 A4 register의 경우 IB1부터 IB15까지는 해당되는 instruction이 없으므로 0으로 되어 있고 IB0에 CALB instruction이 있는데 이 register는 1로 설정 해야 한다.

따라서 그림 7과 같이 index에는 0x00A4로 놓고 value에 0x0001로 놓는다.

그림 6. CALB 및 IM3 signal 설정

그림 7. CALB 및 IM3 signal 설정

18번 register의 경우도 IB1부터 IB15까지는 0이고 IB0에 PSE instruction이 있는데 이 instruction은 0으로 설정한다. 앞에서 한 것과 같이 주소란에 0x0018로 놓고 value간에 0x0001로 놓는다.

PSE는 power supply startup을 enable시키는 bit로 PSE가 1일 때 PSON이 1로 설정된다.

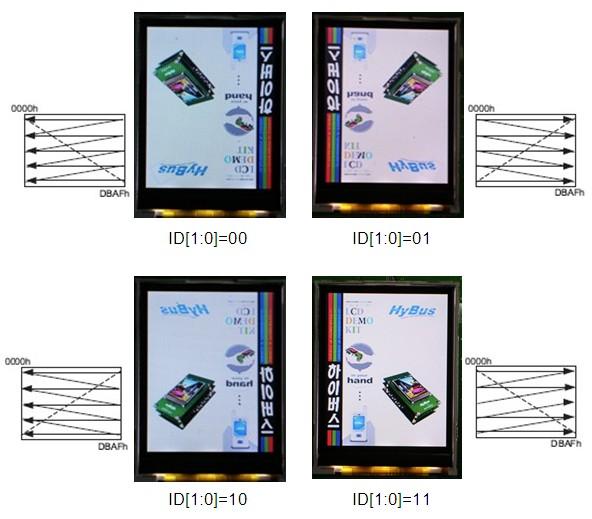

그림 8은 I/D를 변경해보면서 찍은 사진이다. 3번 register를 0x1000, 0x1010, 0x1020, 0x1030 네 가지로 변경하면서 display 해보면 각각의 register에 따라서 Display 방향이 변하는 것을 볼 수 있다.

그림 8. I/D를 변경한 사진

RGB interface

RGB interface는 모니터와 노트북에서 사용하는 VSYNC, HSYNC, ENABLE, DOTCLK 등과 같은 제어 신호를 사용한다. RGB interface는 driver IC의 초기화를 위한 명령어는 CPU interface의 parallel 방식이나 serial 방식으로 전송하고 image data의 경우는 RGB interface로 전송한다.

이러한 RGB interface 신호는 일반적으로 동영상을 많이 사용하는 TFT-LCD에 적용되고 플리커 발생이 적은 장점을 가지고 있다. 또한 CPU interface와 달리 RAM을 사용하지 않아도 되는 장점을 가지고 있다.

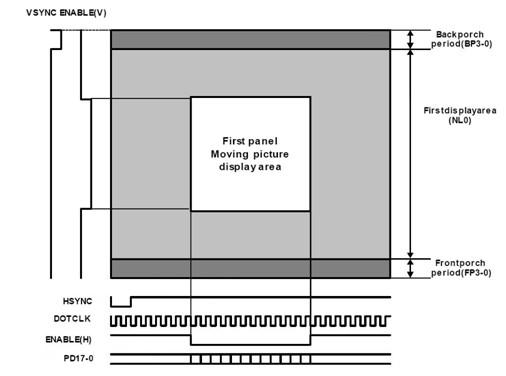

RGB interface의 timing도를 나타내는 그림 9에서 VSYNC 신호는 vertical 동기 신호로 한 frame의 시작을 알리는 신호이다. 한 frame 안에는 horizontal 동기 신호인 HSYNC 신호와 실제 data가 존재함을 알리는 ENABLE 신호가 실제 line 수만큼 존재하게 된다. 보통 VSYNC가 enable 되는 구간의 앞뒤에 back porch와 front porch와 같이 일정한 시간의 non-display 영역을 설정한다.

한 HSYNC timing에는 여러 개의 clock을 가지게 되며 clock 수를 count하여 ENABLE 구간을 설정하고 ENABLE 구간이 active될 때, display data가 표현된다.

그림 9. RGB interface timing diagram

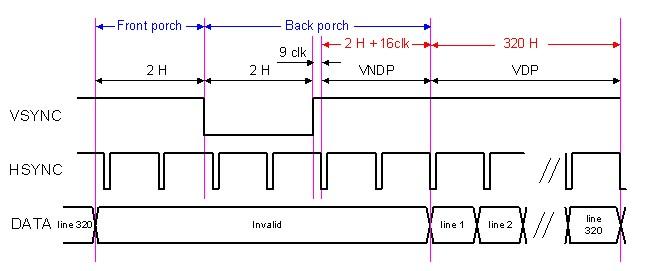

One Frame and Porch 설정

One frame을 결정하는 gate 수는 보통 NL0 instruction을 이용하여 설정하고, RGB interface인 경우, blanking의 구간을 결정하는 back porch와 front porch를 설정한다. Back porch는 BP, front porch는 FP instruction을 이용하며 보통 2 H time으로 설정한다. FP와 BP를 설정할 때는 외부에서 공급하는 RGB interface의 timing도에서의 porch 구간과 일치하도록 설정한다.

그림 10. Frame 및 porch 설정

그림 10 에서와 같이 Vertical Sync 의 VFP, VBP, VSW는 HSYNC가 기준이 되며, Horizontal Sync 의 HFP, HBP, HSW 의 경우에는 Dot Clock의 기준으로 Porch가 결정된다. Vertical Sync , Horizontal Sync 와 Dot Clock의 Sync를 통해서 한 Frame 의 주파수가 결정되고 이런 설정이 맞지 않는다면 LCD 화면에서 flicker현상이나 화면이 밀리는 현상이 나타난다.

Timing

설명

VSYNC

Vertical Sync Polarity 설정으로 Active High, LOW 선택

HSYNC

Horizontal Sync Polarity 설정으로 Active High, LOW 선택

ENABLE

Enable Polarity 설정으로 High, LOW 선택

VBP

Vertical Back Porch

VFP

Vertical Front Porch

VSW

Vertical Sync Width

HBP

Horizontal Back Porch

HFP

Horizontal Front Porch

HSW

Horizontal Sync Width

DCLK

Dot Clock

표 2. RGB Interface timing sync 설정

마치며

이번 호 에서는 Mobile LCD에서 많이 사용하는 CPU interface(I80, M68), RGB interface에 대해서 살짝 알아보았습니다. 현재 사용하는 대부분의 LCD 모듈이 CPU, RGB 방식이라고 생각 하면 됩니다. 다음 호에 소개할 방식은 Serial Interface 인 MDDI, MIPI, I2C 방식인데 이 Interface는 아직 적용된 모듈이 적고, 현재 계속적으로 Version이 발표하고 있는 것이 대부분입니다. 더 자세한 이야기는 다음달에서 하도록 하고… IT 노동자들이야 12시가 넘어야 정신이 돌아 온다는 분들이 있기는 하지만. 전 내일의 노동을 위해서 여기서 마무리 하도록 하겠습니다.

그럼 모든 IT노동자들의 야근이 없는 날을 기원하면서 while(1){ Happiness; }

[출처] Liquid crystal flat panel display - 2. LCD Interface 종류 및 Driver IC 1 (RGB, I80, M68)|작성자 hybusnet

'Electron > Etc.' 카테고리의 다른 글

MIPI-DSI/CSI (0) 2020.07.22 Liquid crystal flat panel display - 3. LCD Interface 종류 및 Driver IC 2 (MDDI, MIPI, SPI, I2C)[출처] Liquid crystal flat panel display - 3. LCD Interface 종류 및 Driver IC 2 (MDDI, MIPI, SPI, I2C) (0) 2020.07.06 DRM, Warter Marking (0) 2018.01.09 이공계 경영학 - 경영정보시스템 (0) 2015.11.28 이공계 경영학 - 경영과학 (0) 2015.11.28